## 41st EOS/ESD Symposium and Exhibits

## September 15 - 20, 2019

Riverside Convention Center 3637 5th St Riverside, CA 92501 USA

Technical Sessions Tutorials Manufacturing Track Workshops

Industry Professionals Social Receptions Contests Exhibition

Co-sponsored by IEEE, EMC Society, The Electron Devices Society, and Reliability Society. Setting the Global Standards for Static Control! EOS/ESD Association, Inc. 7900 Turin Rd., Bldg. 3 Rome, NY 13440-2069, USA PH +1-315-339-6937 • Email: info@esda.org • www.esda.org

## Welcome

Dear EOS/ESD colleagues,

On behalf of EOS/ESD Association, Inc. and the 2019 Symposium Steering Committee, it is my honor to welcome you to the 41st Annual EOS/ESD Symposium and Exhibits at the Riverside Convention Center, in Riverside, California. The EOS/ESD Symposium represents the world's leading forum on Electrostatic Discharge and Overstress. The 41st Symposium awaits you with a dense program packed with tutorials, exhibits, workshops, discussion groups, technical sessions, invited talks, and hands-on sessions. We have maintained the structure of the Symposium in separate design and manufacturing tracks which we started two years ago. In addition, we will follow up on last year's success and organize our second Workshop on Robustness of IoT Devices.

Here is a brief overview of the highlights of the Symposium:

35 Tutorials: World-class experts, in all areas oo EOS and ESD, have been preparing a unique tutorial program. Tutorials

are offered around the Symposium, on Sunday, Monday, and Thursday. In addition to classics on Advanced on-chip Protection, ESD Circuits, and TCAD Fundamentals, we have an increasing focus on System Level Protection, and Electrical Overstress (EOS). New tutorials include System Level ESD/EMI: Principles, Design Troubleshooting, & Demonstrations. Many previously offered tutorials have been refreshed with updated material, including ESD Controls for CDM and Ultra-Sensitive Devices and Circuit Boards.

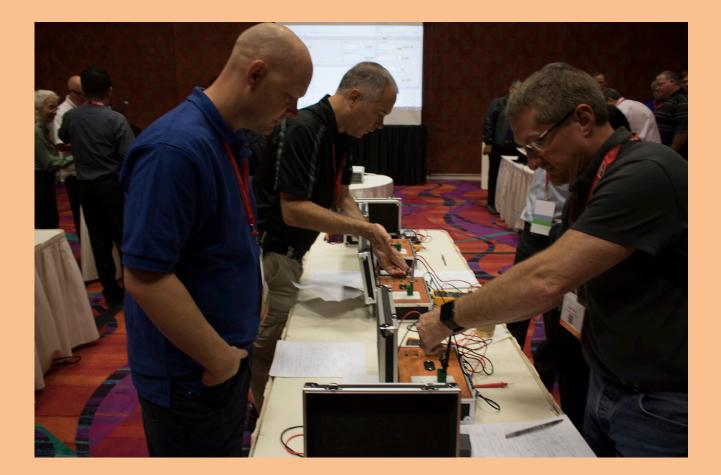

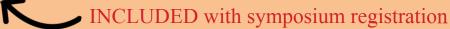

Our industry exhibits display a wide variety of ESD solutions from established products to leading-edge innovations. Representatives from over 40 different companies welcome you to introduce their products and services with the help of short presentations and live demonstrations. The exhibition starts in the exhibit hall during the welcome reception on Monday evening and continues until Wednesday afternoon. The exhibitors offer a unique opportunity for face-to-face discussions with professionals and hands-on experience on static control methods, evaluation techniques, ESD testing hardware, and many other ESD solutions. You can even bring your samples to find out whether a particular solution works for you.

#### Technical Program:

Following the Awards Breakfast, we are proud to present this year's Keynote on "Modeling Systems with Quantum Computing" by Dr. Rudy Wojtecki of the IBM Almaden Research Center.

In the Design Track we will have 30 Peer-reviewed + 1 Invited Technical Paper: These will be presented from Tuesday through Thursday in 12 sessions covering current research topics in the areas of advanced CMOS, RF/HV/MEMS, system-level ESD/ modeling/ soft failures, ESD transient analysis, ESD case studies, EOS/ESD EDA tools, numerical modeling, and ESD testing. The papers are presented by experts from industry and academia driving leading edge research and development.

In the Manufacturing Track we will have 13 Peer-reviewed papers in two technical sessions. Furthermore, the Manufacturing Track includes 2 Sessions with 5 short tutorials, 2 hands-on sessions, and 3 discussion groups.

This year's program again features two year-in-review presentations. Dave Swenson of Affinity Static Control & Consulting will talk about "Test, Evaluate and Support Implantation of Materials, Process and Procedures Used for ESD Control" and Alan Righter of Analog Devices will summarize the "Relationships and interactions between ESD and EMC".

Eight symposium Workshops, which take place on Tuesday and Wednesday evenings, offer an interactive forum for sharing experiences, exchanging knowledge, and exploring potential solutions. The topics cover a wide range from CDM testing to Machine Learning in ESD Check Tools. Even several ESD Myths and Misconceptions will be debunked. Each workshop allows participants the opportunity to learn different perspectives from other colleagues in the field to discuss sometimes controversial topics in an informal environment. Two of the workshops will be held in the popular world café style, which effectively lowers the threshold for every participant to actively engage in a fruitful discussion.

After last year's successful introduction of the "Robustness of IoT Devices" Workshop, we have decided to keep this workshop on the Symposium program. Several invited speakers with unique industry-wide IoT expertise will cover the numerous challenges of meeting reliability and robustness requirements. Join us to learn and network with industry experts.

I most warmly invite every one of you to the General Chair's Reception on Wednesday September 18th from 7:00 PM to 9:00 PM.

The EOS/ESD Symposium is the premier international event for professionals in industry and academia to meet their peers and learn about the latest technical findings and innovative designs. Come, learn, and have fun!

Sincerely, Guido Notermans, Nexperia

2019 EOS/ESD Symposium General Chair

## Table of Contents

| Registration, Fees, Hours                        | 4      |

|--------------------------------------------------|--------|

| General Information                              | 4      |

| Welcome Reception                                | 4      |

| Annual Meeting and Awards Breakfast              | 4      |

| Professional and Technical Women's Reception     | 4      |

| General Chair's Reception                        | 4      |

| Invited Breakfast University Students/Professors | s4     |

| First Time Attendee Social Hour                  | 4      |

| Schedule                                         | 5-7    |

| Keynote                                          | 8      |

| Professional Certification                       | 9      |

| Tutorials                                        | 10-19  |

| Technical Sessions                               | 20-33  |

| Workshops                                        | 34-35  |

| Exhibits                                         | 36     |

| ESDA Officers, Board of Directors, and HQ Staff  | f37    |

| Steering Committee                               | 37     |

| Technical Program Committee                      | 38     |

| Hotel Reservations & Information                 | 39     |

| Registration Form                                | 40-41  |

| Upcoming Announcements                           | .42-43 |

|                                                  |        |

Register Online! http://www.cvent.com/d/86qf9q

#### **On-Site Registration Hours**

Registration will be open at the following times:

| Sunday, September 15                 | 7:30 a.m 5:00 p.m.                |

|--------------------------------------|-----------------------------------|

| Monday, September 16                 | 7:30 a.m 5:00 p.m.                |

| Tuesday, September 17                | 7:30 a.m 5:00 p.m.                |

| Wednesday, September 18              | 7:30 a.m 5:00 p.m.                |

| Thursday, September 19               | 7:30 a.m 5:00 p.m.                |

| Save by registering in advance! This | will facilitate your registration |

| upon your arrival at the Symposium.  | Early registration and mem-       |

ber discounts\* are valid only if received no later than July 15, 2019.

#### Symposium \$800

(Includes technical sessions, workshops, and exhibits) Early Registration Fees valid until July 15, 2019 EOS/ESD Association, Inc. Members\* \$600/Non-Members \$700

#### **Tutorials \$710**

(Sunday, Monday, OR Thursday (Full Day)) Early Registration Fees valid until July 15, 2019 EOS/ESD Association, Inc. Members\* \$510/Non-Members \$610

#### Bundled Fees \$2,465

(Symposium plus Sunday, Monday, and Thursday full tutorial days) Early Registration Fees valid until July 15, 2019 EOS/ESD Association, Inc. Members\* \$1,765/Non-Members \$2,165

#### ESD Program Development and Assessment (ANSI/ESD S20.20) \$1.710

(Attendance limited to first 30 registrants)

This two-day tutorial is not included in the bundled fee. Early Registration Fees valid until July 15, 2019 EOS/ESD Association, Inc. Members\* \$1,510/Non-Members \$1,610

\*Membership discounts apply to those who participate as members all year long and are current at the opening of symposium registration. Memberships processed after this date will not apply. You will receive a complimentary 2020 membership with your Symposium registration which will allow you to enjoy the full benefits of membership in 2020.

Register 5 or more people from one company at the same time and save \$100 per person. Please contact EOS/ESD Association, Inc. prior to registering. Refunds cannot be issued.

#### Student Fees

EOS/ESD Association, Inc., offers a fifty percent discount and waived fees to all Symposium tutorials for full-time students (first author only). Proof of enrollment required. Student fees apply only to symposium and tutorial registration and do not apply to bundled fees or ANSI/ESD S20.20 two day tutorial.

## **General Information**

#### Symposium Proceedings

Each paid registrant receives one electronic copy of the proceedings.

#### **Tutorial Notes**

Customized, full color tutorial notes will be provided to each tutorial registrant.

#### General Chair's Reception

## Duvvury, will present the 2019 Association awards. **Professional and Technical Women's Reception**

The Professional and Technical Women's Reception provides a friendly environment where women in the field of ESD can network and share work experiences. This year's reception will be held on Monday, September 16, from 5:00 p.m. to 6:00 p.m.

#### University Students/Professors Invited to Wednesday Breakfast with ESDA Management

Wednesday, Septmber 18, 7:00 a.m-8:00 a.m

#### First Time Attendee Social Hour

Wednesday, September 18, 12:30 p.m.-1:30 p.m

Guido Notermans invites attendees and exhibitors to the general chair's reception on Wednesday, September 18, from 7:00 pm to 9:00 pm. Poster presentations of technical papers from all sessions will be on display. Don't miss this opportunity to network and share informal conversation with authors, industry professionals, and peers.

#### Register Online! http://www.cvent.com/d/86qf9q

## General Information continued

#### **Hospitality Suites**

To maintain the objectives of the Symposium, EOS/ESD Association, Inc. encourages all exhibitors and guest organizations to schedule their hospitality and other social events at times that do not conflict with the Symposium presentations and educational activities.

#### Age Limits

No one under 18 years of age will be admitted to the exhibit hall.

#### **Unauthorized Solicitation**

Solicitation of business on the premises during the EOS/ESD Symposium by manufacturers or others who are not participating as exhibitors is prohibited.

#### Recording

Video and/or audio recording of Symposium events is prohibited without the prior written authorization of EOS/ESD Association, Inc.

#### Welcome Reception

A welcome reception for all attendees will be held on Monday, September 16, at 6:00 p.m. in the exhibit hall. Network with your colleagues, share your ESD work experiences with others, view the exhibits, or simply pass the time meeting new people and making new friends. The 2019 Steering Committee will greet you and answer any questions regarding the Symposium.

#### Annual Meetings and Awards Breakfast

The annual meeting and awards breakfast for all registered attendees and exhibitors will be held Tuesday, September 17, at 7:30 a.m. Following breakfast, General Chair, Guido Notermans, will officially open the Symposium. Vice General Chair, Lorenzo Cerati, will present the 2018 EOS/ESD Symposium paper awards. Technical Program Chair, Wolgang Stadler, will cover highlights of the 2019 technical program. Association President, Ginger Hansel, will present the Association's annual report. Awards Chair, Charvaka

## SUNDAY, SEPTEMBER 15, 2019

| Registration | 7:30 a.m 5:00 p.m.  |                                                                                                      |

|--------------|---------------------|------------------------------------------------------------------------------------------------------|

| S20.20       | 8:00 a.m 5:00 p.m.  | FC340: ESD Program Development and Assessment (ANSI/ESD S20.20) (PrM) (Day 1)                        |

| Tutorials    | 8:00 a.m 5:00 p.m.  | FC390: Basics of ESD Process Assessment                                                              |

|              | 8:30 a.m 4:30 p.m.  | FC100: ESD Basics for the Program Manager                                                            |

|              | 8:30 a.m 12:00 p.m. | DD103: An Overview of Integrated Circuit ESD: The ESD Threat, Testing, Design Concepts and Debugging |

|              | 8:30 a.m 12:00 p.m. | DD200: Charged Device Model Phenomena, Design, and Modeling                                          |

|              | 8:30 a.m 12:00 p.m. | DD/FC240: System Level ESD/EMI: Principles, Design Troubleshooting, & Demonstrations                 |

|              | 8:30 a.m 12:00 p.m. | FC140: System Level for the Program Manager                                                          |

|              | 1:00 p.m 4:30 p.m.  | DD204: ESD Design in HV Technologies                                                                 |

|              | 1:00 p.m 4:30 p.m.  | DD201: ESD Protection and I/O Design                                                                 |

|              | 1:00 p.m 4:30 p.m.  | DD/FC130: System Level ESD/EMI: Testing to IEC and Other Standards                                   |

|              | 1:00 p.m 4:30 p.m.  | FC220: Device Technology and Failure Analysis for the Program Manager                                |

|              |                     |                                                                                                      |

#### MONDAY, SEPTEMBER 16, 2019 Registration 7:30 a.m. - 5:00 p.m.

| Registration      | 7:30 a.m 5:00 p.m.   |                                                                                   |

|-------------------|----------------------|-----------------------------------------------------------------------------------|

| S20.20            | 8:00 a.m 5:00 p.m.   | FC340: ESD Program Development and Assessment (ANSI/ESD S20.20) (PrM) (Day 2)     |

| Tutorials         | 8:30 a.m 4:30 p.m.   | FC101: How To's of In-Plant ESD Auditing and Evaluation Measurements (PrM)        |

|                   | 8:00 a.m 12:00 p.m.  | DD110: ESD From Basics to Advanced Protection Design                              |

|                   | 8:30 a.m 12:00 p.m.  | DD231: ESD System Level: Physics, Testing, Debugging of Soft and Hard Failures    |

|                   | 8:30 a.m 12:00 p.m.  | DD300: Circuit-Level Modeling and Simulation of On-Chip Protection                |

|                   | 8:30 a.m 12:00 p.m.  | DD115: Latch-up Basics and Testing                                                |

|                   | 8:30 a.m 12:00 p.m.  | FC360: Electrical Overstress in Manufacturing and Test                            |

|                   | 8:30 a.m 12:00 p.m.  | DD/FC380: Electrostatic Calculations for the Program Manager and the ESD Engineer |

|                   | 1:00 a.m 4:30 p.m.   | DD117: TCAD Fundamentals and First Applications to ESD                            |

|                   | 1:00 a.m 4:30 p.m.   | FC121: - Grounding – Variations, Concepts, Nuisances, Equipment & Troubleshooting |

|                   | 1:00 p.m 4:30 p.m.   | DD340: Integrated ESD Device and Board Level Design                               |

|                   | 1:00 p.m 4:30 p.m.   | DD302: Troubleshooting On-Chip ESD Failures                                       |

|                   | 1:00 p.m 4:30 p.m.   | FC200: Packaging Principles for the Program Manager                               |

|                   | 1:00 p.m 4:30 p.m.   | DD/FC165: ESD Control Concepts for Design, Validation, and Test Engineers         |

| Reception         | 5:00 p.m 6:00 p.m.   | Professional and Technical Women's Reception                                      |

| Welcome Reception | n 6:00 p.m 9:00 p.m. | Exhibits Open                                                                     |

|                   |                      |                                                                                   |

## TUESDAY, SEPTEMBER 17, 2019Registration7:30 a.m. - 5:00 p.m.

| Registration       | 7:30 a.m 5:00 p.m.  |                                                                                                                                                                                                            |

|--------------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Awards Breakfast   | 7:30 a.m 9:45 a.m.  | Annual Meeting and Awards Breakfast                                                                                                                                                                        |

| Keynote            | 9:00 a.m 9:45 a.m.  | Modeling Systems with Quantum Computing Rudy J Wojtecki                                                                                                                                                    |

| Exhibits Open      | 9:30 a.m 5:30 p.m.  |                                                                                                                                                                                                            |

| Technical Sessions | 10:00 a.m10:10 a.m. | Exhibitor Showcase in Session 1A and 1B                                                                                                                                                                    |

|                    | 10:10 a.m12:15 p.m. | 1A: Advanced CMOS EOS/ESD and Latch-Up                                                                                                                                                                     |

|                    | 10:10 a.m12:15 p.m. | 1B: Manufacturing I                                                                                                                                                                                        |

|                    | 1:25 p.m 2:50 p.m.  | Hands-On Session I Manufacturing Track                                                                                                                                                                     |

|                    |                     | ESD TR53 - Compliance Verification of ESD Protective Equipment and Materials                                                                                                                               |

|                    | 1:25 p.m 1:35 p.m.  | Exhibitor Showcase in Sessions 2A and 2B                                                                                                                                                                   |

|                    | 1:35 p.m 2:50 p.m.  | 2A: EOS/ESD Failure Analysis, Troubleshooting and Case Studies I                                                                                                                                           |

|                    | 1:35 p.m 2:50 p.m.  | 2B: Full-Custom and Application Driven ESD Concepts                                                                                                                                                        |

|                    | 3:20 p.m 3:30 p.m.  | Exhibitor Showcase in Sessions 3A and 3B                                                                                                                                                                   |

|                    | 3:30 p.m 4:45 p.m.  | 3A: EOS/ESD Failure Analysis, Troubleshooting and Case Studies II                                                                                                                                          |

|                    | 3:30 p.m 4:50 p.m.  | 3B: Manufacturing II                                                                                                                                                                                       |

| Study Session      | 5:00 p.m 6:00 p.m.  | Calculations and ESD Scenarios Review for ESD Program Manager Exam Preparation (STUDY SESSION)                                                                                                             |

| Workshops A        | 5:45 p.m 7:00 p.m.  | A.1 Sub-150V CDM Testing                                                                                                                                                                                   |

|                    |                     | A.2 Machine Learning and More: Advancement in Simulation and EDA methods for ESD Verification<br>A.3 3rd Party IP and Coundry Deliveries – Problem Solved for Seamless, ESD Safe IC Top Level Integration? |

|                    |                     | A.4 EOS Best Practices                                                                                                                                                                                     |

#### WEDNESDAY, SEPTEMBER 18, 2019

| WEDNESDAY, SEPTEMBER 18, 2019 |                    | 18, 2019            |                                                                                     |

|-------------------------------|--------------------|---------------------|-------------------------------------------------------------------------------------|

|                               | Invited Breakfast  | 7:00 a.m 8:00 a.m.  | University Students/Professors Invited to Breakfast with ESDA Management            |

|                               | Registration       | 7:30 a.m 5:00 p.m.  |                                                                                     |

|                               | Exhibits Open      | 8:30 a.m 1:30 p.m.  |                                                                                     |

|                               | Technical Sessions | 8:00 a.m 8:40 a.m.  | Year in Review: Packaging Materials for Shipment of ESD Susceptible Items           |

|                               |                    | 8:55 a.m 9:05 a.m.  | Exhibitor Showcase in Session 4A & 4B                                               |

|                               |                    | 9:05 a.m 11:10 a.m. | 4A: System Level EOS/ESD/EMC I                                                      |

|                               |                    | 9:05 a.m 11:10 a.m. | 4B: Manufacturing III                                                               |

|                               | Reception          | 12:00 p.m 1:30 p.m. | First Time Attendee Reception                                                       |

|                               |                    | 1:40 p.m 1:50 p.m.  | Welcome to the IoT Workshop                                                         |

|                               |                    | 1:50 p.m 4:55 p.m.  | IoT Workshop Session                                                                |

|                               |                    | 1:50 p.m 2:30 p.m.  | Invited Talk                                                                        |

|                               |                    | 2:30 p.m 3:10 p.m.  | Invited Talk                                                                        |

|                               |                    | 3:55 p.m 4:15 p.m.  | Invited Talk                                                                        |

|                               |                    | 4:15 p.m 4:55 p.m.  | Invited Talk                                                                        |

|                               |                    | 1:40 p.m 1:50 p.m.  | Exhibitor Showcase in Session 5A                                                    |

|                               |                    | 1:40 p.m 3:40 p.m.  | Hands On Session II Manufacturing Track                                             |

|                               |                    | 1:40 p.m 1:50 p.m.  | II.A Grounding Measurements                                                         |

|                               |                    | 1:50 p.m 2:00 p.m.  | II.B Assessing the Risk of Insulators and Isolated Conductors                       |

|                               |                    | 2:00 p.m 2:40 p.m.  | II.A, II.B Demo Session                                                             |

|                               |                    | 2:40 p.m 2:50 p.m.  | II.C ESD Field Meter Pitfalls and Voltage Suppression Demonstration                 |

|                               |                    | 2:50 p.m 3:00 p.m.  | II.D Gloves                                                                         |

|                               |                    | 3:00 p.m 3:40 p.m.  | II.C, II.D Demo Session                                                             |

|                               |                    | 1:50 p.m 3:05 p.m.  | 5A: System Level II                                                                 |

|                               |                    | 3:30 p.m 3:40 p.m.  | Exhibitor Showcase in Session 6A                                                    |

|                               |                    | 3:40 p.m 4:55 p.m.  | 6A: Numerical Modeling and Electronic Design Automation I                           |

|                               |                    | 3:55 p.m 5:05 p.m.  | Tutorial Session I: Manufacturing Track                                             |

|                               |                    | 3:55 p.m 4:30 p.m.  | I.A Product Qualification                                                           |

|                               |                    | 4:30 p.m 5:05 p.m.  | I.B Product Qualification vs. Complance Verification                                |

|                               | Workshops B        | 5:20 p.m 6:35 p.m.  | B.1 Adapting to the Demands of Automotive – From an ESD Perspective B.2 IEC Testing |

|                               |                    |                     | B.3 ESD Myths and Misconceptions                                                    |

|                               |                    |                     | B.4 IoT Workshop                                                                    |

|                               | Reception          | 7:00 p.m 9:00 p.m.  | General Chair's Reception Open to all Symposium Attendees and Exhibitors!           |

|                               |                    | b e.ee b            |                                                                                     |

### **THURSDAY, SEPTEMBER 19, 2019**

| Registration       | 7:30 a.m 5:00 p.m.   |                                                                                                    |          |

|--------------------|----------------------|----------------------------------------------------------------------------------------------------|----------|

| Technical Sessions | s 8:00 a.m 8:40 a.m. | Year in Review: Relationships and interactions between ESD and EMC                                 |          |

|                    | 8:55 a.m 10:10 a.m.  | Discussion Group Session Manufacturing Track                                                       |          |

|                    |                      | DG.A The ESD Control Program, AH-HA! I Didn't Think About That!                                    |          |

|                    |                      | DG.B ESD Process Assesment                                                                         |          |

|                    |                      | DG.C ESD Packaging / Reuse of tthe Packaging                                                       |          |

|                    | 8:55 a.m 9:05 a.m.   | Exhibitor Showcase in Session 7A                                                                   |          |

|                    | 9:05 a.m 9:55 a.m.   | 7A: Numerical Modeling and Electronic Design Automation II                                         |          |

|                    | 10:20 a.m 10:30 a.m. | Exhibitor Showcase in Session 8A                                                                   |          |

|                    | 10:30 a.m 12:10 a.m. | 8A: Device Testing: Testing, methods, and Correlation Issues                                       |          |

|                    | 10:35 a.m 12:20 p.m. | Tutorial Session II Manufacturing Track                                                            |          |

|                    | 10:35 a.m 11:10 a.m. | II.A TR2020 Handbook                                                                               |          |

|                    | 11:10 a.m 11:45 a.m. | II.B Measurements Errors and Uncertainties in High Resistance Measurements                         |          |

|                    | 11:45 a.m 12:20 p.m. | II.C Importance of Equipment Verification                                                          |          |

| Tutorials          | 8:30 a.m 12:00 p.m   | DD319: Physical Process, Device, and Circuit Simulation (TCAD) Methodologies in Application to Inc | Justrial |

|                    |                      | ESD Research and Design                                                                            |          |

|                    | 8:30 a.m 12:00 p.m.  | DD260: Design for EOS Reliability                                                                  |          |

|                    | 8:30 a.m 12:00 p.m.  | DD150: Introduction to RF ESD Design                                                               |          |

|                    | 8:30 a.m 12:00 p.m.  | FC120: Ionization Issues and Answers for the Program Manager (PrM)                                 |          |

|                    | 8:30 a.m 12:00 p.m.  | DD/FC250: What Information Needs to be Exchanged for Potential EOS Problem                         |          |

|                    | 8:30 a.m 12:00 p.m   | FC210:ESD Standards Overview for the Program Manager                                               |          |

|                    | 1:00 p.m 4:30 p.m.   | DD220: Transmission Line Pulse (TLP) Basics and Applications (DD)                                  |          |

|                    | 1:00 p.m 4:30 p.m.   | FC365: Practical Applications of Ionization                                                        |          |

|                    | 1:00 p.m 4:30 p.m.   | FC150: Hands-on ESD Measurements & Instruments - Uses and Pitfalls                                 |          |

|                    | 1:00 p.m 4:30 p.m.   | FC166: ESD QMS Best Practices Strategy Including Class 0 and Costly Controversial ESD Myths        |          |

|                    | 1:00 p.m 2:30 p.m.   | DD381: Electronic Design Automation (EDA) Solutions for ESD                                        | 0        |

|                    | 3:00 p.m 4:30 p.m.   | DD382: Electronic Design Automation (EDA) Solutions for Latch-up                                   | 6        |

|                    |                      |                                                                                                    |          |

# FRIDAY, SEPTEMBER 20, 2019 8:00 a.m. - 5:00 p.m. De 8:00 a.m. - 5:00 p.m. Pro

8:00 a.m. - 5:00 p.m.Device Design Certification Exam8:00 a.m. - 5:00 p.m.Program Manager Certification Exam

### Modeling Systems with Quantum Computing Rudy J. Wojtecki, IBM

The physical realization of multiqubit quantum computers (QCs) are extremely challenging as it requires the ability to control, manipulate and accurately measure an element exhibiting a quantum behavior. Recent work has demonstrated this with superconducting transmon gubits that behave like artificial atoms, acting as the guantum element capable of displaying properties of like superposition and entanglement but are macroscopic in size and composed of elements that can be handled in existing semi-conductor fabrication methods. While efforts to improving the quality of these devices have yielded progress to providing more powerful quantum computers capable of addressing more and more complex problems. While these QCs are a nascent technology, even on a system composed of 6 gubits IBM reported the development of software and uses the unique QC hardware that enabled the accurate modeling guantum systems H2, LiH and BeH2. Furthermore, the use of QC in a variety of simulations have been demonstrated that have implications in machine learning as well as artificial intelligence. As QC systems scale, the ability to simulate increasingly complex, and more useful, quantum systems will be realized. This talk will provide an introduction to QC hardware and the ability to exploit these systems in modeling complex systems.

Dr. Wojtecki graduated from Case Western Reserve University in 2013 with a Ph.D. in Macromolecular Science & Engineering under the auspices of Stuart J. Rowan (now at the Univ. of Chicago) and the support of a NASA GSRP fellowship. Dr. Wojtecki joined IBM – Almaden Research Center after completion of his graduate work, as an engineer, and promoted to Research Staff Member in 2015. He is author of 23 peer reviewed scientific publications including a Nature Materials Review article with more than 800 citations. In 2017 he was recognized as an IBM Master Inventor for work high-lighted in over 100 patent and patent applications. Dr. Wojtecki's current research efforts are geared to address the fabrication of superconducting qubits for quantum computers and ongoing challenges for lithographic materials used in the manufacturing of semiconductors.

#### **EOS/ESD Association, Inc. Professional Certification**

EOS/ESD Association, Inc. offers professional certification for ESD control program managers and device design technical specialists.

#### ESD Certified Professional-Program Manager

The impact of the ANSI/ESD S20.20 ESD control program standard on the global industry has been extraordinary. As a result, EOS/ESD Association, Inc. recognizes the need to offer a certification program for individuals that are involved in designing, implementing, managing, and auditing ESD control programs in their facilities. The program manager certification program serves that purpose. In addition, the needs of the technical community for certification of various technical specialists are apparent.

Requirements for certification include attending required prerequisite tutorials and passing a final exam. All of the prerequisite courses cannot be completed by attending only the 2019 Symposium. Details of the certification program are also available at the registration desk.

The preferred tutorial sequence for the program manager curriculum is:

|    | COURSE TITLE                                                                      | FACE TO FACE TUTORIAL                        | ONLINE         |

|----|-----------------------------------------------------------------------------------|----------------------------------------------|----------------|

| 1  | FC100: ESD Basics for the Program Manager                                         | Symposium, Sunday, Sept. 15                  |                |

| 2  | FC101: How To's of In-Plant ESD Auditing and Evaluation Measurements              | Symposium, Monday, Sept. 16                  |                |

| 3  | FC110: Cleanroom Considerations for the Program Manager                           |                                              | Online Academy |

| 4  | FC120: Air Ionization Issues and Answers for the Program Manager                  | Symposium, Thursday, Sept. 19                | Online Academy |

| 5  | FC200: Packaging Principles for the Program Manager                               | Symposium, Monday, Sept. 16                  | Online Academy |

| 6  | FC210: ESD Standards Overview for the Program Manager                             | Symposium, Thursday, Sept. 19                | Online Academy |

| 7  | FC140 - System Level for the Program Manager                                      | Symposium, Sunday, Sept. 15                  | Online Academy |

| 8  | FC220: Device Technology and Failure Analysis for the Program Manager             | Symposium, Sunday, Sept. 15                  | Online Academy |

| 9  | DD/FC380: Electrostatic Calculations for the Program Manager and the ESD Engineer | Symposium, Monday, Sept. 16                  | Online Academy |

| 10 | FC340: ESD Program Development & Assessment (ANSI/ESD S20.20<br>Seminar)          | Symposium, Sunday & Monday, Sept. 15<br>& 16 |                |

#### ESD Certified Professional-Device Design

ESD device design certification was developed for individuals that are involved in designing, testing, characterizing, and implementing improved ESD protection designs. Device design certification demonstrates knowledge, experience, and competency in the area of ESD design and test for device protection.

Requirements for certification include attending required prerequisite tutorials and passing a final exam. All of the prerequisite courses are not available in the 2019 Symposium tutorial program. Details of the certification program are also available at the registration desk.

The preferred tutorial sequence for the device design curriculum is:

|    | COURSE TITLE                                                                                             | FACE TO FACE TUTORIAL            | ONLINE         |

|----|----------------------------------------------------------------------------------------------------------|----------------------------------|----------------|

| 1  | DD110: ESD Basics for Advanced Protection Design                                                         | Symposium, Monday, Sept.<br>16   |                |

| 2  | DD301: SPICE-Based ESD Protection Design Utilizing Diodes and Active MOSFET Rail<br>Clamp Circuits       |                                  |                |

| 3  | DD211: EOS/ESD Failure Models and Mechanisms                                                             |                                  |                |

| 4  | DD102: On-Chip ESD Protection in RF Technologies                                                         |                                  | Online Academy |

| 5  | DD200: Charged Device Model Phenomena, Design, and Modeling                                              | Symposium, Sunday, Sept. 15      | Online Academy |

| 6  | DD112: Latch-up Fundamentals                                                                             |                                  | Online Academy |

| 7  | DD300: Circuit-Level Modeling and Simulation of On-Chip Protection                                       | Symposium, Monday, Sept.<br>16   |                |

| 8  | DD302: Troubleshooting On-Chip ESD Failures                                                              | Symposium, Monday, Sept.<br>16   |                |

| 9  | DD120: Device TestingIC Component Level: HBM, CDM, MM, and TLP                                           |                                  |                |

| 10 | DD311: Impact of Technology Scaling on ESD High Current Phenomena and Implications for Robust ESD Design |                                  |                |

| 11 | DD220: Transmission Line Pulse (TLP) Basics and Applications                                             | Symposium, Thursday, Sept.<br>19 |                |

| 12 | DD/FC130: System Level ESD/EMI: Testing to IEC and other Standards                                       | Symposium, Sunday, Sept. 15      | Online Academy |

#### **ESDA Certification Exams**

The certified professional program manager and device design exams will be held on Friday, September 20. To take the exam, applicants must have a registration form on file with EOS/ESD Association, Inc. headquarters complete with a \$50 filing fee prior to the Symposium.

### **TUTORIALS: SUNDAY & MONDAY, SEPTEMBER 15-16**

## FC340: ESD Program Development and Assessment (ANSI/ESD S20.20)

8:00 a.m. - 5:00 p.m. *Kevin Duncan, Seagate Technology; David E. Swenson, Affinity Static Control Consulting, LLC* Certification: PrM

This seminar provides instruction on designing and implementing an ESD control program based on ANSI/ESD S20.20. The course provides participants with the tools and techniques to prepare for an ESD facility audit. This two-day course is an ESDA certification requirement for in-plant auditors and program managers who are working toward professional ESD certification. The following topics are covered in this course:

- Overview of ANSI/ESD S20.20

- How to approach an assessment

- Administrative elements

- ESD program assessment

- · ESD program techniques for different applications

- Technical elements

- Overview of the assessment process

- The audit checklist and follow-up questions

It is recommended that the ESD Program Development and Assessment (ANSI S20.20) be taken after the certification candidate has taken most of the other program manager related tutorials.

### **TUTORIALS: SUNDAY, SEPTEMBER** 15

### FC100: ESD Basics for the Program Manager

8:30 a.m. - 4:30 p.m. *Ron Gibson, Advanced Static Control Consulting* Certification: PrM

This tutorial provides the foundation material for understanding electrostatics and ESD and their role in the manufacturing and handling of ESD sensitive devices. The fundamental properties of charge, electric fields, voltage, capacitance, and current are discussed with a view towards understanding key electrostatic phenomena and electrical processes. These include charge generation and decay, material properties, and induction. An overview of device failure mechanisms is presented, including how these models impact ESD control programs. Finally, the course provides an overview of ESD control procedures during handling and manufacturing and an overview of ANSI/ESD S20.20 program requirements. This full day course is required for those in-plant auditors and program managers who are working toward professional ESD certification. The presentation includes many in-class demonstrations, videos, and animated slides.

Some sample topics covered in this course are:

- · Definitions and relationships among important electrical and mechanical properties

- Causes of charge generation and decay

- Field effects and voltages

- Role of capacitance in ESD (Q=CV)

- · Overview of key measurements including common pitfalls of some measurements

- Review of ESD failure models

- · Understanding and demonstrating electrostatic induction

- Utility and limitations of air ionization

- Basic goals of ESD controls

- · Properties of effective ESD control products and materials

- · Overview of ANSI/ESD S20.20 ESD program development requirements

#### Customized, full color tutorial notes will be provided to each tutorial registrant.

## **TUTORIALS: SUNDAY, SEPTEMBER 15** FC390 - Basics of ESD Process Assessment

8:00 a.m. - 5:00 p.m. Reinhold Gaertner, Infineon Technologies; Wolfgang Stadler, Intel Deutschland GmbH

This tutorial gives an introduction to the approach and measurement methodologies for ESD process assessment and ESD risk analysis in typical production processes in semiconductor, printed-circuit board (PCB), and electronic system manufacturing industries. It summarizes the relevant physical parameters (e.g., resistance, charge, electric fields, capacitances, resistances, discharge currents, and ESD event detection by EMI) and discusses their influence on the ESD risks caused by charged personnel, charged devices and boards, and ungrounded conductors. Measurement techniques are explained in detail together with their limitations for the different process steps and strategies for an efficient ESD risk assessment. The application of those measurement techniques to assess possible ESD risks and to solve ESD problems are explained using theoretical and real-world case studies from each of the processes mentioned above. Examples of possible mitigation strategies are discussed with the attendees. The tutorial includes practical demonstrations and a hands-on session for the attendees to get experience and learn pitfalls of the most important measurement techniques used in ESD process assessment.

## DD200: Charged Device Model Phenomena, Design, and Modeling

8:30 a.m. - 12:00 p.m. Michael Chaine, Micron Technology, Inc.; Melanie Etherton, NXP Semiconductors

Certification: DD

This course teaches basic ESD circuit design concepts and ideas required to design ESD protection for charge device model (CDM) ESD tests. The course covers a brief history of CDM ESD development, charge and discharge physics, characterization methods, CDM failures mechanisms, and CDM design-in strategies.

CDM ESD circuit design approaches and simulation setups for CDM failure debugging are presented in this tutorial on the basis of case studies. Insight into CDM circuit simulation requirements and physical aspects of the CDM ESD phenomenon that are important for reproducing the event with circuit simulation will be taught, and modeling approaches for CDM specifi c device physical effects necessary for accurate circuit simulation will be introduced. This course also teaches methods for simplifi ed CDM circuit simulations where detailed information is either not available or too complex to simulate.

The course focuses on what type of circuits fail during a CDM discharge event and teaches the different types of ESD design circuit strategies that can be applied to protect those circuits. This class covers basic to advanced topics for CDM ESD design, but the student is assumed to already have a basic understanding of the CDM test method.

## DD103 - An Overview of Integrated Circuit ESD: The ESD Threat, Testing, Design Concepts and Debugging

8:30 a.m. - 12:00 p.m. Alan Righter, Analog Devices

Many Integrated Circuit (IC) designers do not have a working knowledge of ESD. This tutorial presents aspects of ESD that are relevant to IC designers and will enable them to improve their first time right ESD track record. This tutorial will also be useful for a wide range of specialists including layout designers, I/O designers, test engineers, failure analysis engineers, quality and reliability engineers, and architects as well as ESD design engineers just entering the field. The student will learn the fundamentals of ESD design, know the variables which affect ESD robustness, understand that ESD design needs to be addressed early in the design cycle and be better able to interact with ESD design specialists, understand ESD testing and interpret failure analysis data.

## **NEW** DD/FC240 - System Level ESD/ EMI: Principles, Design Troubleshooting, & Demonstrations

8:30 a.m. - 12:00 p.m. Jay Skolnik, Skolnik Technical Training Certification: PrM

System level ESD tutorial about how to reduce ESD effects on systems (boards, chassis, etc.). Real circuits will be demonstrated in class showing techniques to correct the detrimental effects. Theory and real-life examples from recent past will be used to substantiate the methods.

Customized, full color tutorial notes will be provided to each tutorial registrant.

### **TUTORIALS: SUNDAY, SEPTEMBER 15**

## FC140 - System Level for the Program Manager

8:30 a.m. - 12:00 p.m. John Kinnear, IBM Corporation Certification: PrM

This tutorial is intended to help those tasked with testing products to IEC and other system level ESD standards by providing detailed information on IEC 61000-4-2, the most widely used standard, and highlighting the harmonization and differences among IEC, ANSI, Telcordia, and some automotive ESD standards. We will answer common questions regarding test set-ups, test points, and procedures, and address key issues, including: 1) Differences between "verification" and "calibration" and when is each required; the influence of ESDA WG14 technical report (TR) on IEC and how it affects the calibration and verification procedures. 2) Test set-up requirements, the test environment, ground connections, and return paths and ground plane effects. 3) Testing procedures with demonstration on actual products, how the tester affects test results, and problems with test result variations due to simulator influences. 4) What points need to be tested and why, guidance on determining "operator accessible" points and ports, exempted points and ports, and what to do around connectors and connector pins. 5) ANSI and other ESD standards, the drive toward harmonization with IEC, why standards will probably never be the same as IEC, and the scope of different standards. This system level ESD tutorial will cover several facets of ESD as applied to electronic systems.

### **DD204: ESD Design in HV Technologies**

1:00 p.m. - 4:30 p.m.

Lorenzo Cerati, STMicroelectronics; Ulrich Glaser, Infineon Technologies AG

This tutorial gives an introduction to ESD design in high voltage technologies for integrated circuits with pin voltages from 12 volts upwards. After a short introduction of typical applications and requirements, an overview of different technologies and the typical device portfolios in these technologies will be given. Different ESD protection concepts are introduced, analyzing advantages and disadvantages of the various possible approaches to implement ESD networks (diodes, snapback devices, active clamps, etc.). Finally, HV technology and design related challenges regarding ESD protection are discussed, with a special focus on the formation of parasitic bipolar devices and the impact on the circuit's ESD performance. The attendee will gain a good basic knowledge of the main characteristics of HV technologies, the different ESD protection concepts, and ESD protection challenges that are specifi c for HV technologies. This will be a help for understanding and further development of HV ESD protection. An extensive literature list is provided for further study of various subjects regarding HV ESD.

## **DD201: ESD Protection and I/O Design**

1:00 p.m. - 4:30 p.m. Michael Stockinger, NXP Semiconductors

This tutorial is intended to provide the attendees with the tools to take a device and circuit level understanding of ESD protection methods and implement them effectively in I/O designs for CMOS bulk technologies. Beginning with a review of common ESD protection strategies, this course will focus more directly on how to build ESD-robust I/O cells and how to integrate them on a full chip. The tutorial will cover various types of I/O pads including analog, RF, and digital pads. Different types of ESD protection strategies and their usage in I/O pad cells will be described, for example, rail clamp, self-contained, and SCR based protection schemes. This course will also discuss the decisions and challenges which ESD and I/O designers typically face when designing I/O pads. More complex ESD solutions will also be described such as stacked rail clamps, ghost rails, and protecting signals that can swing below ground or above the supply. Finally, this tutorial will touch on various supply schemes including multiple power domains and isolated grounding schemes. It will end with discussing pad ring construction aspects for both wire-bond and flip-chip packages.

## DD/FC130 - System Level ESD/EMI: Testing to IEC and Other Standards

1:00 p.m. - 4:30 p.m. *Jeff Dunnihoo, Pragma Design, Inc.* Certification: DD

This tutorial is intended to help those tasked with testing products to system level ESD standards by providing first an overview of how real-world system ESD events are simulated in different standards and testers in general, and then provide detailed information on IEC 61000-4-2, the most widely used standard. This introduction will highlight the similarities and differences between IEC, ANSI, Telcordia, and some automotive ESD standards. We will answer common questions regarding test setups, test points, and procedures, and address key issues, including: 1) differences between "verification" and "calibration" and when is each required; 2) test equipment requirements, the test environment, ground connections, return paths, and ground plane effects. 3) Testing procedures with demonstration on actual products, how the tester and procedure affects test results, and problems with test result variations due to simulator influences; 4) definitions of testing failure criteria for the product; 4) what points need to be tested and why, guidance on determining "operator accessible" points and ports, exempted points and ports, and what to do around connectors and connector pins. 5) ANSI and other ESD standards, the drive toward harmonization with IEC, the scope of different standards, and why they are unlikely to converge. This system level ESD tutorial will cover different perspectives on ESD as applied to electronic systems from the user's, the designer's, and even the designer's competitor's points of view.

## **TUTORIALS: SUNDAY, SEPTEMBER 15** FC220 - Device Technology and Failure Analysis for the Program Manager

1:00 p.m. - 4:30 p.m. *Terry Welsher, Dangelmayer Associates, LLC* Certification: PrM

This tutorial provides an overview of the device technology used to provide ESD protection, ESD protection techniques, and Failure Analysis (FA) techniques to debug non-working ESD protection. This class does not go into the depth necessary to equip the student to be an ESD Protection Designer or an ESD Failure Analysis Engineer. It does familiarize the student with the terms and concepts of ESD protection and FA to allow the student to interact and understand the work being done by the Designer or Failure Analyst. After completing this tutorial the student should be able to understand the basics of device ESD protection design and some of the trade-offs inherent in that process. The student should also be familiar with the most commonly used failure analysis techniques and tools used to identify the root cause of an ESD failure. The topics covered include: the three most common ESD Models: HBM, CDM and System Level (IEC); characteristics of ideal ESD protection; ESD failure analysis schemes; key characteristics of real ESD protection; failure analysis flow; failure analysis tools and how they are applied to ESD failures.

## **TUTORIALS: MONDAY, SEPTEMBER 16** FC101: How To's of In-Plant ESD Auditing and Evaluation Measurements

8:30 a.m. - 4:30 p.m. *Ted Dangelmayer, Dangelmayer Associates, LLC* Certification: PrM

Compliance verification is one of the most important elements of ESD program management and there are many technical and administrative pitfalls that can be avoided. The attendee will learn not only how to make valid auditing measurements in accordance with ESD TR53 - Compliance Verification of ESD Protective Equipment and Materials, but also how to recognize and avoid common pitfalls. Common instruments will be explained as well as the invalid test results that can result when they are used incorrectly. Advanced auditing techniques will also be covered that enable Class 0 devices to be handled successfully. There are many ways to administer effective compliance verification programs. Two successful examples will be presented that were developed independently by different companies. Hidden administrative pitfalls that often result in poor compliance will also be discussed. This tutorial will be highly interactive with live demonstrations, in-plant photographs, and compelling video clips. Students will be encouraged to ask questions and to participate in the discussions.

#### **TUTORIALS: MONDAY, SEPTEMBER 16**

## DD110: ESD From Basics to Advanced Protection Design

8:00 a.m. - 12:00 p.m. *Charvaka Duvvury, ESD Consulting, LLC* Certification: DD

This course gives a comprehensive overview from ESD basics to ESD on-chip design principles, covering up to the latest silicon technologies appealing to a variety of engineers from design to process technology, and failure analysis to quality. The attendee will have an in-depth understanding of the principles of ESD device design along with a full perception of what it takes to address almost every kind of design scenario, how to apply rules of thumb for successful on-chip design, knowledge of lessons learned from case studies, and empowerment to communicate with customers on ESD quality issues. In its complete ESD overview, the course offers emphasis on on-chip protection methods including an understanding of any interactions to the eventual system protection.

## DD231: ESD System Level: Physics, Testing, Debugging of Soft and Hard Failures

8:30 a.m. - 12:00 p.m. David Pommerenke, University of Missouri-Rolla

The tutorial is an expanded version of the previous DD231 tutorial on system level ESD. The main difference is the addition of many experimental demonstrations, update of information, and in-depth discussion on problems of the IEC 61000-4-2 testing, with examples on how to perform this testing and obtain the best possible results and documentation. About half of the time will be spent on experimental demonstrations. Topics will include:

- ESD physics: charging and discharging.

- System level ESD testing

- · System level soft failure mechanisms and debugging

- Design for avoiding ESD problems

### DD300 - Circuit-Level Modeling and Simulation of On-Chip Protection

8:30 a.m. - 12:00 p.m.

*Elyse Rosenbaum, University of Illinois at Urbana-Champaign* Certification: DD

This tutorial addresses modeling of on-chip ESD protection devices and simulation of ESD protection networks. The primary focus is SPICE-type simulation with compact (physics-based) models but a general survey of modeling approaches and simulation techniques will also be provided. The physical operating principles of commonly-used ESD protection devices will be examined. The high-current characteristics and transient responses of those devices will be explored to ascertain what behaviors should be captured by a model intended for circuit-level simulation of ESD.

Specific examples of model implementations will be provided. Techniques for circuit-level modeling of self-heating will be presented. Parameter extraction and model scalability will be addressed. This tutorial assumes some familiarity with device physics. It is directed toward persons with interests in semiconductor device physics, electronic design automation, and on-chip ESD protection circuit design.

## **REVISED** DD115: Latch-up Basics and Testing

8:30 a.m. - 12:00 p.m. Marty Johnson, Texas Instruments, Inc.

This tutorial will introduce the participant to the basics of latch-up stress testing. The course will cover basic latchup theory, basic latch-up mitigation techniques, the JEDEC Latch-up Standard (JESD78) and discuss the effects of the standard on stress testing methodology. Also, there will be a discussion of possible differences in set-up when stress testing between digital, mixed signal and analog products. Examples of these set-ups will be described and discussed to aid the student better apply the methods in their stressing environment. Interpretation of the stress data will be described. The future of the standard will also be discussed and how that may impact the philosophy of stressing. This tutorial can be very helpful for a variety of people in the semiconductor industry including circuit designers, product engineers, test engineers, failure analysts, quality / reliability engineers and technicians supporting latch-up stressing.

#### **TUTORIALS: MONDAY, SEPTEMBER 16**

## FC360: Electrical Overstress (EOS) in Manufacturing and Test

8:30 a.m. - 12:00 p.m. Reinhold Gaertner, Infineon Technologies

Electrical overstress (EOS) is a major cause of device failure in manufacturing and in the field. Despite this, there is relatively little information on the sources of EOS and on prevention practices, particularly for the factory. In this tutorial, the fundamentals of device overstress are reviewed. Relationships among device EOS stressing models, such as the Wunsch-Bell curve, are discussed. The causes of EOS and EOS-like events in manufacturing are described and categorized by source and by stress-type. The difficulties in distinguishing between power-induced EOS and high current ESD events such as charged-board events (CBE) and cable discharge events (CDE) are discussed. Case histories, including failure analysis and root cause determination, are presented and the few relevant industry specifications are reviewed.

## **REVISED** DD/FC380 - Electrostatic Calculations for the Program Manager and the ESD Engineer

8:30 a.m. - 12:00 p.m. Terry Welsher, Dangelmayer Associates, LLC

This tutorial focuses on the basic calculations and techniques of use to the program manager and the ESD engineer. The content is at the introductory college pre-calculus and introductory college physics level set in the context of electrostatic discharge and its effects. It is suggested that the student gain some familiarity with these subjects prior to the tutorial. Topics covered include the electric force, the electric field and Coulombs law, electric potential, and voltage. Gauss' Law is discussed as it relates to the electric field, induction, and the Faraday cup. The capacitance in Q = CV is used to explain charge sharing. RC decay is discussed as it relates to ESD discharge from humans, devices, wrist straps, and materials. After completing this course, the attendee should leave with a proper understanding of the differences among the calculations for peak current, power, energy, and threshold voltage for a simple device.

## **REVISED** DD117 - TCAD Fundamentals and First Applications to ESD

1:00 p.m. - 4:30 p.m. Kai Esmark, Infineon Technologies

TCAD (technology computer aided design) tools have become an indispensable utensil for the semiconductor industry. The possibilities to analyze, predict and optimize a certain semiconductor device behavior through modeling semiconductor fabrication (Process TCAD) and semiconductor device operation (Device TCAD) are countless. This includes the area for ESD and Latch-up development, as early access to fundamental device parameters under very high current density and high temperature transients is the key to overcome the conceptual problem of concurrent engineering for ESD engineers.

This tutorial serves as a basic introduction into TCAD tool chain including process and device simulation as well as the creation and integration of compact models for mixed more simulation. Focus points are the capabilities but also limitations of these tools, like the requirements for a 2D/3D simulation approach and the validity of the models describing the fundamental physics, especially in the high temperature regime.

## DD340 - Integrated ESD Device and Board Level Design

1:00 p.m. - 4:30 p.m. Harald Gossner, Intel Deutschland GmbH

The tutorial is a hands-on training course for performing a simulation based optimization of PCB ESD protection design and provides deep understanding of the relevant performance criteria both of TVS diodes and IO circuits. The presented method follows the system effi cient ESD design (SEED) approach as recommended by the Industry Council on Target Levels and JEDEC.

The method allows the achievement of correct first time PCB builds and reduces the respin effort for boards and ICs. Based on a TLP characterization of SoC interface circuits and TVS diodes, simulation models for impedance and clamping behavior, as well as failure threshold, are extracted. These are used to assess design solutions by transient simulations. This is showcased by real world examples.

### **TUTORIALS: MONDAY, SEPTEMBER 16** DD302 - Troubleshooting On-Chip ESD Failures

1:00 p.m. - 4:30 p.m. Hans Kunz, Texas Instruments Certification: DD

Diagnosing and fixing on-chip ESD product qualification failures can often be one of the more challenging aspects of work in ESD. The pressure to quickly find and correct an HBM/MM/ CDM failure in order to qualify a product often compounds the inherent difficulty of troubleshooting. Experience diagnosing failures, though not desirable from a product qualification standpoint, can greatly improve troubleshooting skills. This tutorial will build troubleshooting experience and skills by presenting case studies of actual on-chip HBM failures in a workshop format. The evidence for each case will be revealed and the failure analyzed in the same manner as an actual failure. Participants will be led through and allowed to analyze each failure case, interacting with the instructor to determine its root cause and a solution. This tutorial will identify common concepts, methods, and tools useful in failure diagnosis. Participants should be familiar with CMOS technology, on-chip ESD breakdown phenomena, standard ESD protection circuits, and the HBM test procedure. Participants should also be acquainted with basic CMOS circuit design, should be able to read circuit diagrams, and should have a basic understanding of the function of IO circuits.

## DD/FC165 - ESD Control Concepts for Design, Validation, and Test Engineers

1:00 p.m. - 4:30 p.m. *Ginger Hansel, Dangelmayer Associates, LLC*

Design Engineers strive to incorporate ESD protection into chip designs, but they are often unclear about the best way to handle the physical devices. The Industry Council on ESD Targets documented a need to lower both the HBM and CDM thresholds with the confidence that factories already had the appropriate ESD control programs in place. However, many engineering labs do not understand or follow industry ESD guidelines and are unaware of the potential jeopardy created by these lower thresholds. Anyone doing device testing, characterization, TLP stress testing, board level analysis or upgrading their own computer should know basic ESD control techniques. This seminar will include practical ESD control tips for engineering labs as well as how to set up and monitor a comprehensive ESD control program. Real world examples will show the increased ESD risk of Charged Board Events (CBE), the surprising damage due to hand tools and how to use event detectors to identify ESD threats.

You've spent a lot of effort doing careful designs – now take good care of your valuable test chips and prototype engineering samples.

## **NEW** FC200 - Packaging Principles for the Program Manager

1:00 p.m. - 4:30 p.m. Craig Zander, Transforming Technologies

Shipping electronic parts within a factory, to another factory, distributor, or to an end-user has always been an area of uncertainty within the manufacturing process.

To provide clear-cut information on what type of controlled packaging should be used in any situation, EOS/ESD Association, Inc. released a comprehensive revision of the obsolete industry standard EIA 541-1988. The newer document, ANSI/ESD S541, is the focus of this inclusive session. It provides information and guidance, as well as material specifications, to assist in the design and implementation of a packaging plan for use within an ANSI/ESD S20.20 based ESD control program. Current and newly released test method standards suitable for packaging material evaluation will be described. Course credit applies to the ESD program manager certification curriculum. Previous attendance at the "FC100: ESD Basics" and "FC101: How To's" tutorials are highly recommended.

## **NEW** FC121 - Grounding – Variations, Concepts, Nuisances, Equipment & Troubleshooting

1:00 p.m. - 4:30 p.m. Jay Skolnik, Skolnik Technical Training

Grounding for ESD control seems so simple, yet many times issues arise after a grounding strategy is implemented. This class will cover variations in grounding approaches, concepts to consider when employing a ground system, nuisances and how to troubleshoot them with the correct equipment.

### DD260: Design for EOS Reliability

8:30 a.m. - 12:00 p.m. Charvaka Duvvury, ESD Consulting, LLC

During the design of on-chip protection and latch-up immunity, the consequences to EOS damage susceptibility are often overlooked. This class aims to fi rst clearly establish the nature of EOS and some of the common causes for unintended EOS, followed by the on-chip IC design styles that can lead to EOS damage and customer returns. By way of illustrative examples and case studies, these potential issues are highlighted. These include the designs in low voltage CMOS, mixed voltage technologies, analog designs, and high voltage designs. Some mention of automotive applications leading to EOS and the automotive perspective will also be covered. Finally, the design rules to follow for EOS mitigation; as well as on-going communication tips with customers to achieve these objectives, will be reviewed.

The course aims to give a clear understanding of EOS events, the defi nition of EOS related to on-chip design principles, design improvements to overcome EOS return rates, check lists for EOS avoidance, and tips for customer communications.

## **NEW** DD150 - Introduction to RF ESD Design

8:30 a.m. - 12:00 p.m. Kathleen Muhonen, Qorvo

This tutorial is an introduction to RF concepts and RF ESD clamp design. It is intended for ESD engineers who do not have an RF background to come up to speed on the concepts needed to design effective protection circuits. The RF concepts include impedance matching and smith chart basics. RF amplifier operation and load line basics are presented to give a foundation for the RF ESD protection circuit design. The tutorial will also touch briefly on RF switches and filters. The second half of the tutorial will focus on how to design an ESD clamp for an RF application. Concepts will be presented such as calculating the turn-on voltage of the clamp such that it will protect the part but not turn on during normal, RF operation. A clamp's parasitics also needs to be considered in an RF application so that the parasitics do not degrade the product's performance. Finally, some testing tools will be reviewed with respect to testing RF products. The challenges will be highlighted and different testing practices that are used in HBM, TLP and IEC testing of RF products will be reviewed.

## DD319 - Physical Process, Device and Circuit Simulation (TCAD) Methodologies in Application to Industrial ESD Research and Design

8:30 a.m. - 12:00 p.m. Vladislav Vashchenko, Maxim Integrated Corp.

Over the last two decades numerical simulation with commercially available technology CAD (TCAD) tools has been widely applied across industry and research organizations to address ESD protection design challenges, ESD solutions development, test chip design and validation of the device, clamp circuits, and application circuit blocks as well as interpretation of the failure analysis results. Corresponding significant and diverse material has been accumulated in the literature and unpublished industry practices. At the same time the best practices and methodologies were not adequately summarized to bring them a broader audience in an easily accessible and practical, usable way. As a result, these are way underused today. The purpose of this tutorial is provide a comprehensive structured review of the published ESD TCAD results and construct a step-by-step approach to successful methodology and best practices application. The presented material achieves this goal in several steps: (i) means of review and classification of the most relevant studies where the ESD problems have been addressed through TCAD simulation; (ii) derivation of a generic physical simulation workflow based upon either process simulation or parameterized device definition followed by device simulation and mixed-mode analysis in ESD time domain; (iii) outlining and classifying the major application physical ESD problems which can be addressed through 2D or 3D TCAD analysis. The presentation material is supported by numerous easy-tounderstand simulation examples.

## DD/FC250 - What Information Needs to be Exchanged for Potential EOS Problem

8:30 a.m. - 12:00 p.m. Reinhold Gaertner, Infineon Technologies; James Roberts, Stoneridge, Inc.

EOS-like damages represent a significant percentage of components returned by the OEM's to tier1 and semiconductor manufacturers for comprehensive failure analysis in the automotive industry. There is generally a requirement from the OEM to conduct a detailed investigation to determine the root cause of the failure; however, commonly this cannot be done due to missing information and poor communications but blocks a lot of capacity. This tutorial presents information based on case studies why it is not possible to find the root cause for an EOS-like damage without an information sharing between all tier levels. Based on the new guideline a two level support will be introduced based on an information sharing between the OEM, tier1 and semiconductor manufacturers that can lead to a higher chance to identify the root cause of the damage and allows to focus on the important topics.

## FC120 - Ionization Issues and Answers for the Program Manager

8:30 a.m. - 12:00 p.m. *Kevin Duncan, Seagate Technology* Certification: PrM

The primary method of static charge control is direct connection to ground for conductors, static dissipative materials, and personnel. Air ionization is also part of a static control program to deal with the problems of isolated conductors and insulating materials. This seminar is a basic course on ionizers, providing an introduction to their use, as well as application information. It examines common problems caused by static charge and the need for ionizers in a static control program. Types of ionizers, their use environments, and performance test methods using the Ionization Standard will be demonstrated. Installation, safety, maintenance, and contamination issues will be presented. Finally, case histories will be analyzed illustrating the use of ionizers in a variety of work environments.

## FC150: Hands-on ESD Measurements & Instruments-Uses and Pitfalls

1:00 p.m. - 4:30 p.m. Ginger Hansel, Dangelmayer Associates, LLC

Accurate data is the foundation of effective ESD program management. This hands-on tutorial will explain and demonstrate the proper use of ESD test equipment such as static locators, resistance meters, charge plate monitors, and event detectors. We will examine pitfalls of using these common instruments that can result in an incorrect representation of the ESD risk. For example, static locators can give misleading readings if the effects of voltage suppression are not taken into account. We will also discuss the effective use of ionization since ionizers that are not measured, maintained, and located correctly may contribute ESD hazards to the work area. Each student will participate in class exercises to perform these tests. The hands-on experience is the best way to understand the seriousness of the pitfalls and the benefits to taking the proper precautions. What you learn will help you avoid frequent auditing problems and improve your compliance verification program.

## **NEW** FC210 - ESD Standards Overview for the Program Manager

8:30 a.m. - 12:00 p.m. *Craig Zander, Transforming Technologies* Certification: PrM

The ESD Association's introduction of the Program Manager Certification curriculum has created a need to modify the Standards Tutorial that has been presented for a number of years, mainly to help individuals prepare for the iNARTE Engineering and Technician Exams. Currently, many of the ESDA Standards and Standard Test Methods are discussed in depth in the individual tutorials related to the specific subject matter. This Standards Tutorial provides an overview of all the Standards, grouped into common test types, based on measurement probe and test instruments. A common methodology is used in this tutorial to cover the requirements, applications and specifications for each Standard and Standard Test Method.

## DD220: Transmission Line Pulse (TLP) Basics and Applications

1:00 p.m. - 4:30 p.m. Evan Grund, Grund Technical Solutions, Inc. Certification: DD