# Discontinuing Use of the Machine Model for Device ESD Qualification

Charvaka Duvvury, Texas Instruments

Robert Ashton, ON Semiconductor

Alan Righter, Analog Devices

David Eppes, AMD

Harald Gossner, Intel Mobile Communications

Terry Welsher, Dangelmayer Associates

Masaki Tanaka, Renesas Electronics Corporation

#### Foreword:

The Machine Model test, as a requirement for component ESD qualification, is being rapidly discontinued across the industry. This memo is intended to illustrate why MM evaluation is not necessary for qualification. The following major conclusions can be made about MM in general:

- ❖ MM is redundant to HBM at the device level since it produces the same failure mechanisms, and the two models generally track each other in robustness and in failure modes produced.

- ❖ The MM test has more variability than HBM due to the MM's greater sensitivity to parasitic effects in the tester circuitry.

- ❖ There have not been any significant engineering studies (with verified data) which could be used to establish required passing level

- ❖ The test method was incorrectly given the name "Machine Model", though no firm unique connection between the model and actual machine-induced device failures was ever established. In fact the model was developed as a "low-voltage HBM".

- CDM does a better job of screening for fast metal-to-metal contact events than MM

- ❖ The vast majority (>99%) of electrical failures in manufacturing correlate to CDM and EOS, and not MM

- ❖ MM testing has not shown any additional failures not explained by CDM, HBM or EOS

- ❖ MM testing consumes resources and creates time-to-market delays while providing no additional failure modes or protection strategies which HBM and CDM already cover.

❖ It is important to understand the scope of this memorandum. It summarizes what has been learned about the test method *only*. The information summarized here in no way diminishes the importance of adequate grounding of any metal which may come in contact with ESD-sensitive devices and the importance of the avoidance of hard metal-metal discharges.

## A. Background to the Issue:

As will be explained below, the Machine Model (MM) is a widely <u>misunderstood</u> <u>component ESD qualification test method.</u> It continues to generate confusion for both OEM customers and their IC suppliers during ESD qualification. Many companies and design organizations continue to use MM, mostly as a legacy "required" practice, despite the fact that it has been downgraded by three standards bodies and is no longer recommended for qualification testing in accordance with JEDEC JESD47. The automotive industry, a longtime user of this method, no longer requires it in their AEC-Q100 list of qualification tests. The scopes of the JEDEC (JESD22-A115) and ESDA (ANSI/ESD STM5.2) test method documents have also been changed to reflect this status. There are a number of reasons for these changes, as will be outlined below. The continued use of MM for qualification based solely on legacy requirements has no technical merit given the information that has been gathered over the last few years. Those companies who continue to use MM will take on an unnecessary and burdensome business approach. The reasons against use of the MM are given below.

- 1. Historically speaking, the 200pF, "0 ohm" model which later became known as the machine model originated from several Japanese semiconductor corporations as a worst-case representation of the Human Body Model (HBM). The model was later presumed by some, because of the lower discharge impedance, to simulate abrupt discharge events caused by contact with equipment and empty sockets (functional test, burn-in, reliability testing, pick and place operations, etc). This happened at a time when the very fast rise time of metal-metal discharges was not well-understood. Since that time, the Charged Device Model (CDM) has been proven to quite adequately cover these events.

- 2. Recently, M. Tanaka-san (Renesas Electronics) at the September 2011 JEITA meetings [3] presented rationale and data supporting the elimination of the MM test. According to his historical account, the so-called Machine Model originated at Hitachi (now Renesas Electronics) about 45 years ago and was introduced to Japanese semiconductor customers as a test case to represent the HBM test in their IC product test report. This test method spread widely to the Japanese customer base and was later established as an ESD test standard by the EIAJ in 1981. Around 1985 some began onwards mistakenly to refer to the test as the Machine Model. Then, starting in 1991, ESDA, JEDEC and IEC adopted the model and its name as a new test standard. As use of the model increased, it was realized that the Machine Model name caused a lot of misunderstanding that needed to be clarified.

- 3. In the early days of ESD device testing there was also a desire to avoid the high precharging voltages of the HBM test (2kV and higher), and the 200pF and low impedance of the "MM" was thought to be an equivalent but safe lower voltage test to address the same failure mechanisms as HBM. However, establishment of a single translation from MM voltage to HBM voltage has been difficult to achieve. Protection design has traditionally been focused on meeting the HBM requirement, but MM testers are susceptible to parasitic circuit elements; these parasitics from relay switching networks in the simulators cause more variation in the MM waveform than waveforms from HBM testers. In spite of this and without any supporting data, 200V MM became established as a de facto requirement. It was thought to be the safe level for handling and that this level had to be simultaneously met along with the de facto 2kV HBM standard. In reality a device with a 2kV HBM withstand voltage might have an MM withstand voltage anywhere from 100 to 300V, depending on the device characteristics and the MM tester parasitics. This lead to much of the confusion associated with specifying both HBM and MM specification levels.

- 4. The next important reason for discontinuing MM is that fast discharges to or from a metal surface are not correctly represented by the MM. The characteristics of the MM rising pulse were not established based on comparison to measurements on machine pulses but rather were determined by characteristics of the already developed HBM simulators. The fast rising leading edge of metal-to-metal discharges are actually more effectively simulated using the current standard CDM test methods. This is known today because of the development of high speed oscilloscopes. However, during the 1980s there was a misunderstanding that MM was a good representation for CDM. This misunderstanding actually delayed the eventual development and acceptance of the CDM standards used today. Later in the 1990s, with the much improved and accurate test for CDM and with the wider recognition that the fast discharges are covered by CDM alone, the test for MM became more frequently replaced with CDM.

#### B. MM vs. HBM and CDM

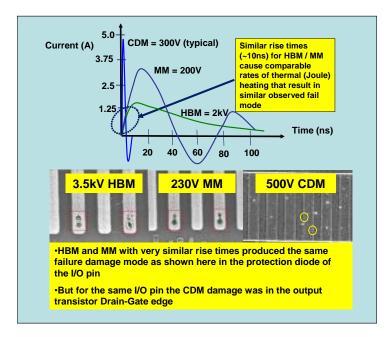

The waveforms for HBM, MM and CDM are compared in Figure 1. The HBM and MM have similar ranges of rise time (2-10ns). Therefore any thermal heating in silicon taking place in this time period leads to the same failure mechanisms for both models. This holds true for all technologies, including advanced technology nodes. This early part of the waveform determines where protection circuits must be deployed in design. With similar rise time characteristics, HBM and MM encourage the same protection designs. For CDM, on the other hand, the rise time is much faster (0.1 – 0.5 ns) and often leads to a unique failure mechanism like oxide breakdown. Even more important, the observed ESD field failures are dominated by oxide breakdown when the CDM level is not adequate. Thus, a different set of protection strategies are generally needed for CDM. This makes it even more critical to focus on CDM qualification, instead of duplicating the HBM test information by using the MM. In Figure 1 we also show the observed failure modes for the same I/O pin after stressing with HBM, MM, and CDM.

It is clear that with HBM and MM the damage sites were the same, in the protection diode, but with CDM stress the damage site corresponds to oxide breakdown in the output transistor. This also illustrates the fact that meeting high levels of MM does not improve the CDM performance until the right effective design techniques are employed.

Figure 1. Comparison of HBM, MM, and CDM Waveforms.

Commercial MM testers have inductors built into the MM stimulus circuit. These inductors must be present to produce the oscillatory waveform required in the MM test method. The inductors, however, actually slow down the MM waveform (Figure 1), and therefore MM cannot represent very fast metal-to-metal contact discharge as CDM does. On the other hand, the CDM test is directly represented by elevating the package potential and directly grounding the pin to produce the fast discharge. MM cannot be relied on to accurately model fast metal to metal contact discharges, which are known to occur in the field.

## C. Metal Discharge versus CDM Discharge

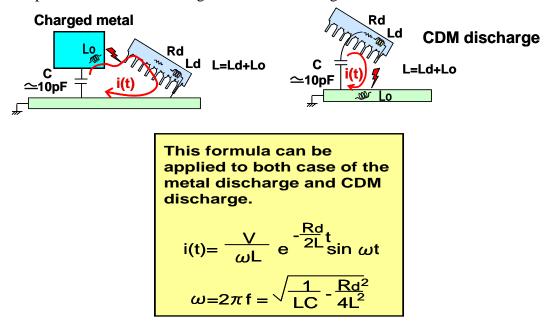

The analysis of M. Tanaka [4] is shown here to demonstrate that a metal discharge from a small metallic object to a device is similar to the commonly used CDM test. Tanaka considers small objects because large machines (typically >10 pF) are almost always grounded for reasons beyond ESD and thus pose little practical threat for these events. On the other hand, tools and small machines are difficult to ground and may lead to charging effects where the capacitance of the metal object is related to surface area and distance. These values can range from <1pF to nearly 10 pF. For example, this could be as much as 1pF for a small metal object of 10 cm<sup>2</sup> at a distance of 0.5 cm. Both the small metal discharge and the CDM discharge can be represented by the same set of equations for I(t), and thus both can be expected to generate the same discharge event if

the values of the parameters are similar. Figure 2 illustrates the case for a small object of 10 pF for both metal discharge and CDM discharge.

Figure 2. Discharge current equation for metal discharge or CDM discharge [3.]

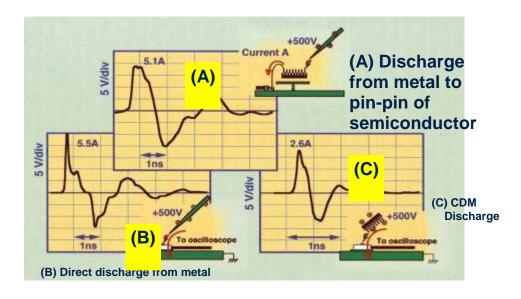

The above analysis is confirmed by measurements [4] as shown below (Figure 3) where the discharge in (A) from a charged tweezer to IC pin is the same as direct discharge from metal as shown in (B), and both are similar to the generated CDM discharge in (C). The time scale for both metal discharge and CDM discharge are indeed the same clearly indicating that CDM is a good representation of the metal discharge in the EPA.

Figure 3. Comparison of measured waveforms for metal discharge and CDM discharge events [4]: (A) discharge from a charged tweezer on pin, (B) direct discharge from metal and (C) CDM test discharge.

- **❖** Metal discharge events are well represented by the CDM test.

- ❖ Most of the field failure returns for ESD have been replicated by the CDM test but none known with the MM test that are not also produced by HBM.

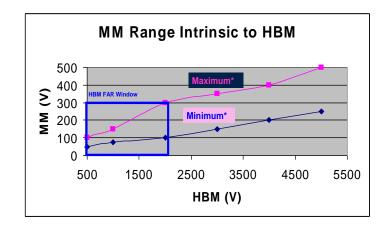

The Industry Council on ESD Target Levels has studied the HBM and MM results on a wide variety of designs in many technologies and has concluded that MM is intrinsically related to HBM, with a correlation factor "range" that is dependent on the HBM design level [1]. This data is represented in Figure 4. However, the most important conclusion of the study was that MM is a redundant test and that a sufficient level of MM robustness is automatically included in an adequate HBM design. This also includes the bipolar nature of the MM stress. Any oscillatory waveform which might be measured during discharges in the field is sufficiently covered, if the part is proven to have an adequate HBM design.

This minimum design value, as measured by a MM tester, is well above any voltage remaining on all properly grounded machines in an ESD protected manufacturing environment. In essence, meeting a safe value for HBM (and CDM) is sufficient for production of ICs without needing to evaluate MM as an additional qualification.

- **The Machine Model test method specification to qualify ICs does not model or advance the real world ESD protection of IC products**

- **The Example 2** IC evaluation with MM does not give any additional information as to how to address machine ESD control

- \* While MM is an unnecessary qualification test, it is important to emphasize that control of voltage on machine parts that might contact device pins in accordance with ESD programs specifications such as S20.20 programs is still important.

Figure 4. Correlation between HBM and MM measured on the same devices.

### D. Field Data Analysis

The work from the Industry Council has shown that most of the overstress field returns exhibit failure signatures of higher energy EOS, and that the level of HBM ESD from 500V to 2000V (shown as the HBM Failure Analysis Return (FAR) window in Figure 2) on 21 billion shipped units did not show a correlation to the customer field return rates. Similarly, these very same shipped units (500V to 2kV HBM) also had MM levels in a range between 50-300V, as also seen from Figure 2. Therefore it can be concluded that the EOS field returns are indeed not related to this range of intrinsic MM levels. That is, it does not matter if a shipped device has a measured MM value of 50V or 300V.

**Devices with various measured MM levels have shown no correlation to real world EOS failure returns.**

#### E. Standards Bodies and Positions on MM

During the last two decades the electronics industry's standards bodies have changed their viewpoint with regard to MM and its requirement for IC qualification. At present, JEITA in Japan does not recommend MM. The Automotive Electronics Council's AEC Q100 standard gives a choice between HBM and MM, but does require CDM. In recent years JEDEC has strongly recommended discontinuing use of the MM for ESD qualification because of its test variability and non-correlation to real world failure modes. In general, standards bodies have come to recognize that:

- **<u>IC Qualification to HBM and CDM provides all the necessary ESD test requirements</u>**

- **MM** testing of ICs is redundant to HBM and does not reflect unique real world component ESD failure modes.

- **Billions of IC components have been shipped worldwide and qualified** using HBM and CDM testing only. No field failures have been found that would have been prevented by additional MM qualification.

The following statements are from the JEDEC web site:

- **❖** "JESD22-A115B is a reference document; it is not a requirement per JESD47G (Stress Test Driven Qualification of Integrated Circuits)."

- **❖** Machine Model as described in JESD22-A115B should not be used as a requirement for IC ESD Qualification.

- **❖** Only human body model (HBM) and charged device model (CDM) are the necessary ESD Qualification test methods as specified in JESD47G."

The ESD Association has downgraded the MM document from a Standard (S5.2) to a Standard Test Method (STM5.2)[5] and has adopted the following position:

The ESD Association does not recommend using MM ESD as described in STM5.2 for IC qualification. IC Qualification should be done using the current standard HBM and CDM methods.

#### F. Conclusions

The information in this document supports the discontinuation of MM as part of IC qualification. The most important point to note is that a wide range of products, having only HBM and CDM testing performed, are being shipped today at volume levels in the billions, with no field returns due to ESD. These products, passing at or above the recommended minimum HBM and CDM levels, are being routinely shipped by major suppliers, and are accepted by major OEMs. No increase in field return rates has been observed with MM removed from qualification for these products.

The confusion generated by MM has persisted in the industry for over two decades. The presumed need for this test is causing additional qualification delay due to an extraordinary consumption of design / test resources, added delays in time-to-market, and in some cases having an impact on IC speed and performance. Maintaining safe HBM and CDM levels is sufficient to meet all IC manufacturing, handling and assembly needs.

## G. Epilogue

Different customer sectors may feel that they need enhanced ESD requirements for specific reasons. For example, some automotive customers have more consistently required MM model testing; the impression being that an independent and redundant test provides enhanced safety, improved quality and reduced defectivity. However, industry experience has shown that passing a redundant (to HBM) MM qualification test does not help automotive manufacturers achieve these goals. Meeting current industry standard HBM / CDM will insure that a product can be safely handled with sufficient margin to prevent ESD damage and maintain the quality/reliability of the product as shipped from the component manufacturer. Since many suspected ESD failures turn out to be higher energy EOS in nature, methods to prevent electrical overstress during manufacturing will also help maintain product reliability.

#### H. Common Goals

We have presented evidence and arguments that the MM test of ICs is redundant and there is no proof that devices have failed in the field because MM evaluation was not done. We strongly recommend that this test be discontinued for ESD qualification. This will save the semiconductor industry a tremendous and an unnecessary burden by greatly reducing the routine characterization that is done to support the qualification process. The ESD robustness designed into integrated circuits to survive HBM and

CDM testing will provide protection against any MM-like stress. Eliminating MM testing of ICs has no deleterious effects and will free up resources for more important engineering challenges.

#### **References:**

- [1]. JEP155, "Recommended Target Levels for HBM/MM Qualification," at <a href="http://www.jedec.org">www.jedec.org</a> and at <a href="http://www.esdtargets.blogspot.com/">http://www.esdtargets.blogspot.com/</a>

- [2] K.T. Kaschani, M. Hofmann, M. Schimon, M.W. Wilson and R. Vahrmann, "On the Significance of the Machine Model', ESDForum2007, Munich, Germany, 4-5 December 2007.

- [3] M. Tanaka, JEITA/JEDEC Meetings, Tokyo, September 2011.

- [4] M. Tanaka, K. Okada, and M. Sakimoto, "Clarification of Ultra-high-speed Electrostatic Discharge and Unification of Discharge Model," EOS/ESD Symposium, pp, 170-181, 1994.

- [5] ESDA standards document definitions and hierarchy are summarized at <a href="www.esda.org/Documents.html">www.esda.org/Documents.html</a>

Founded in 1982, the ESD Association is a professional voluntary association dedicated to advancing the theory and practice of electrostatic discharge (ESD) avoidance. From fewer than 100 members, the Association has grown to more than 2,000 members throughout the world. From an initial emphasis on the effects of ESD on electronic components, the Association has broadened its horizons to include areas such as textiles, plastics, web processing, cleanrooms, and graphic arts. To meet the needs of a continually changing environment, the Association is chartered to expand ESD awareness through standards development, educational programs, local chapters, publications, tutorials, certification, and symposia.