Integrating Embedded ESD Detection, Part 3

In Part 1 and Part 2 of this series, we explored the opportunities for embedded on-chip and system-level ESD detection solutions. We introduced embedded detection technology and considerations for balancing ESD detection solutions with ESD protection requirements.

In Part 3, we will outline the steps to consider when embedding ESD detection capabilities into your system and overall design flow.

Choosing the Right Technology

Selecting the appropriate embedded ESD detection technology is crucial. On-chip, discrete, software detection, or a combination of strategies may be the best choice for your application. Consider the following factors:

- ESD Event Types: Evaluate the types of ESD events your device will most likely encounter and what levels should be detected. Ensure that the chosen technology can detect and record or respond to these events effectively.

- ESD Failure Criteria: Map out the expected ESD event failure mechanisms and recovery modes. Separate hard failures and soft upsets and how the device should respond to them, even if they are outside of the robustness limits for the product. For example, if your device’s intended robustness level is exceeded and this is detected, should it do a recalibration or self-test, or should it “brick” itself and report potential malfunction? A medical or aerospace device may have a different “warranty” behavior than a low-cost consumer product.

- Speed Requirements: Assess the speed at which ESD events need to be detected and responded to in your application. Some applications may have faster response times for safety or process than others.

- Integration Complexity: Evaluate the complexity of integrating the technology into your chip design versus adding discrete components to the system. Consider the data collection paths, such as fan-in registering, boundary scan chains, GPIO, or A/D multiplexers. Some solutions may require more extensive modifications to your design than others.

- Cost Considerations: Compare the cost of implementing different embedded ESD detection technologies, factoring in both development and manufacturing costs.

- Compatibility with EDA Flow: Collaborate with experienced library providers to guarantee the smooth integration of your chosen technology into your design process. Even if your primary expertise lies in making your application function effectively, it is important to acknowledge the numerous distinctive challenges that come with “rolling your own” ESD protection, not to mention the added complexity of ESD detection.

Integrating Embedded ESD Detection Technology

Once you’ve outlined your integrated or discrete protection and detection goals, it’s time to implement them and eventually adapt the decision and optimization process into your design flow. Here’s a step-by-step guide.

Step 1: Technology Selection

Begin by selecting the specific embedded ESD detection technology that aligns with your design requirements. If you’ve chosen embedded detection or similar technology, consult with the library provider for detailed integration guidelines. For discrete solutions, simulate the detector circuit options with appropriate ESD injection models and validate them with mock-ups in the ESD lab. A small evaluation board with LED or audio indicators for detector output are simple and convenient options in the ESD lab where you don’t want to risk expensive oscilloscopes and IDE interfaces to ESD damage.

Step 2: Design Modifications

Adapt your chip design (and flow) or system PCB to accommodate the selected technology. This may involve:

- Layout Adjustments: Modify the chip/board layout to include ESD sensors at strategic locations. Ensure that these sensors are adequately connected to the monitoring and response circuitry, accounting for the noisy EMI environment expected during a strike.

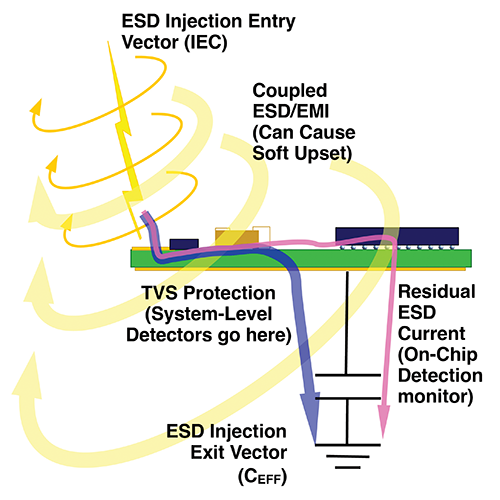

- Be the Bolt: Identify the entry/exit vector(s) of concern. Find a place to attach a voltage, current, or near-field probe to the discharge path in order to trigger your detector. (See Figure 1.)

- Circuit Modifications: Integrate the technology’s response mechanisms into your circuitry, ensuring that they can be triggered promptly upon ESD event detection.

Figure 1: Consider the entry/exit vector and where to place the detectors.

Figure 1: Consider the entry/exit vector and where to place the detectors.

Step 3: Simulation and Verification

Before moving to fabrication, perform simulations to validate the functionality of your embedded ESD detection system:

- ESD Event Simulation: Simulate ESD events of varying magnitudes and polarities to verify that the embedded detection system reliably detects and responds to them. Do not waste time inventing your own ESD pulse model. Select the appropriate one from the dozens of industry-developed ESD pulse spice models available in the literature.

- Response Testing: Ensure that the system’s response time and level ranges meet the requirements of your application.

- False Positive/Negative Analysis: Evaluate the system’s performance in terms of false positives (incorrectly detecting an ESD event due to non-ESD EMI, for example) and false negatives (failing to detect a genuine ESD event).

Step 4: Layout Optimization

Optimize your chip or board’s layout to minimize parasitic capacitance and ensure efficient signal routing. In many cases, the existing ESD protection can be used to trigger detection without any additional parasitic burden.

Step 5: Collaboration with EDA and Library Providers

Collaborate closely with EDA tool providers to facilitate the integration of the embedded ESD detection technology into your design flow. Ensure that simulation and verification tools are compatible with other transient models from other device vendors in your system. Since this is a leading-edge technology, be persistent. Designing simple ESD protection systems remains a specialized area of expertise. Frontline support and application engineers may not have received training in ESD detection technologies yet.

Step 6: Documentation

Thoroughly document the integration process, including detection goals, limitations, layout modifications, circuit changes, and simulation results. This documentation will be invaluable for troubleshooting and future reference. Don’t forget to keep your firmware group in the loop! Programmers do not like to be told that memory or program counters may suddenly change due to ESD in otherwise normal operation, so help them embrace this scary concept and give them a handle on how to identify the event (ISR or POR vector) and how to recover the hardware state after a detection event (Consider machine states such as Figure 2.)

Figure 2: What state are you in?1

Figure 2: What state are you in?1

Validation and Testing

Validation and testing are critical phases in the implementation of embedded ESD detection. These steps help ensure that the technology performs as expected and provides the necessary protection for your design. Here’s how to approach this phase.

Importance of Validation

Effective validation of the detectors is essential for building confidence in your embedded ESD detection system’s reliability, but also the detection system can be used to help validate the on-chip and external system-level ESD protection robustness.

One problem of cutting-edge chip-level characterization has been the scarcity of early functional samples of “golden” qualification chips and early validation system boards. Many of these chips and evaluation boards are critically allocated to software development or other functional requirements and cannot be sacrificed for ESD or other potentially destructive transient testing.

Embedded transient scanning detectors may be designed to trigger at various levels of applied stress and may, therefore, provide an early “warning track” of imminent failure. Traditional step-testing of a system can begin from a harmless starting point and be increased incrementally until near-destructive levels are detected, allowing testing to be aborted before damage occurs. The guardbanding of the target robustness level can be validated in this way without destroying the device.

Testing Methodologies

Consider the following testing methodologies for embedded ESD detection:

- ESD Generator Testing: Use ESD generators to emulate ESD events and verify that the embedded detection system responds appropriately. Test under various conditions, including different magnitudes and polarities of ESD strikes. Carefully document the detector levels and ranges that correspond to different strike levels applied at different injection points.

- Multi-strike ESD Robustness Testing: Subject the semiconductor chip to a series of ESD events to determine its robustness and ability to continue functioning under ESD stress. While some stress levels will precipitate instantaneous damage, other types of latent damage can accumulate after repeated strikes at much lower levels.2

- Temperature and Voltage Testing: Test the embedded detection system under extreme temperature and voltage conditions to ensure its reliability across different operating environments.

Real-World Testing Scenarios

To ensure that your embedded ESD detection technology can handle real-world scenarios, consider testing in environments where ESD events are likely to occur. These could include testing during product handling, manufacturing, and everyday use. Additional telemetry of event severity and frequency across deployed products in the field can provide invaluable information on the actual application environment. This can reveal actual levels in the field that can help optimize or cost-reduce protection goals.

Conclusion

In Part 1 of this article series, we explored the critical need for embedded ESD detection in the context of advanced semiconductor nodes. The vulnerabilities of advanced ICs to ESD damage have necessitated the development of innovative solutions, such as embedded detection technology, to augment protection schemes. Embedded detection’s real-time monitoring and response capabilities offer a new level of overall robustness and reliability by expanding the visibility of ESD events and effects.

In Parts 2 and 3, we’ve provided engineers and designers with an overview of embedding ESD detection in their products and processes. Embedded ESD detection gives you more visibility and flexibility, allowing you to optimize cost, enhance performance, and bolster robustness as semiconductor technology advances.