Voltage to Current Correlation for CDM Testing

New Approaches for CDM Testing

MAY 1, 2024

It is now well known that testing for CDM ESD evaluation is becoming a bigger challenge. Previously (In Compliance Magazine, March 2021), capacitively coupled TLP (CCTLP) was described as an alternate approach. It offers many advantages compared to the standardized field-induced CDM setup according to the JS002 standard [1]. Testing of a package, bare die, or wafer is enabled with high reproducibility. The failure correlation between CDM and CCTLP has been investigated based on peak current stress levels and not by a charging voltage level [2]. If testing with an alternative CDM method as CCTLP is done to reproduce JS002, the CDM charging voltage must be transferred into peak current levels.

Device and Tester Capacitance

A measure for the severity of the CDM stress is the effective capacitance Ceff of a device [3]. Ceff characterizes the amount of exchanged charge between DUT and test setup at a specific stress level (e.g., VCDM) in a specific testing environment.

Products can be categorized with respect to Ceff in an FICDM setup because of the direct relation to the peak current for a given test voltage, as described in [4].

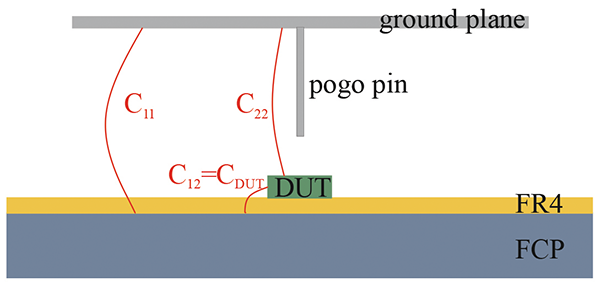

During a CDM stress, different capacitance values play a role according to the three-capacitances model, as shown in Figure 1.

Figure 1: Three-capacitances-model of the CDM tester

Figure 1: Three-capacitances-model of the CDM tester

The three capacitance values determine the effective capacitance Ceff. The DUT capacitance CDUT is defined as the capacitance from the device to the field plane. The static capacitance value for CDUT is extracted from a Finite Element Method (FEM) simulation according to the three-capacitances model shown in Figure 1. Differences between Ceff and CDUT capacitances either extracted from FEM-simulation or calculated as parallel plate capacitance Cplate (A is the area of the DUT, and d is the thickness of the FR4 dielectric layer) are demonstrated based on the metallic circular coin modules (height 1.27 mm, diameters see Table 1).

| P1 | P2 | JS | P4 | JL | P5 | P6 | P7 | P8 |

| 2.29 | 4.49 | 8.89 | 18.03 | 25.37 | 36.05 | 43.04 | 51.02 | 62.52 |

Table 1: Coin diameter in mm, height of coin: 1.27 mm

Figure 2: Ceff, CDUT, and Cplate related to the area of coins

Figure 2: Ceff, CDUT, and Cplate related to the area of coins

The FEM simulation of CDUT does not coincide with the simple plate capacitor formula since fringing effects are also considered, especially for small devices. CDUT also shows a linear dependency on the area-capacitance relation. In contrast, Ceff values show saturation with increasing area or volume of a DUT. As a result, not only the area of the bottom surface contributes to the capacitance but also the sidewalls and, therefore, the volume.

Impact of Device Dimensions

To calculate the CDM discharge current from the volume, the device area is considered as the maximum edge length a x b, including the pins and mold compound (Figure 3). For a bare die product that does not go into a final package, the area is calculated from the edge length of the silicon accordingly.

Figure 3: Definition of device area A=a x b and volume V=A x h

Figure 3: Definition of device area A=a x b and volume V=A x h

Statistical analysis of CDM testing data shows the relevance of device area and volume for predicting stress current levels in a CDM test since the height h of the device has a non-neglectable influence on the discharge current. A database with over 15 million CDM waveforms has been used to evaluate the relation between area, volume, peak current, and the effective capacitance Ceff. The area and volume of about 10000 different device types can be derived from the package dimensions included in the database. For each device type, only the waveforms are evaluated, showing the maximum positive peak current Ipeak out of several CDM discharges for a positive charging voltage level of 500 V. According to the measurement results, the peak current reduces with the increasing height of the device.

This can be shown using the set of nine cylindrical solid metal coins P1 to P8 with different diameters and volumes (see Table 1)[5]. The coin reference for the peak current still gives a reasonable orientation for the maximum peak current. Figure 4 shows the dependency of the effective capacitance Ceff on the volume. For very flat packages, the limit of the coins is exceeded but still gives a meaningful value. The coin with the smallest volume and, therefore, lowest Ceff reaches the lowest peak current and vice versa. For devices, this means that their Ceff with the according current can be related to the current of the coins. As shown, the device height is becoming relevant for the estimation of the stress current level, therefore, the volume is introduced as the preferred parameter. Thus, the volume value can be used to estimate the expectable peak current with respect to the coin values as shown in Figure 5.

Figure 4: Effective capacitance vs. device volume for h>1.27mm. The influence of the device height on the effective capacitance is illustrated per color.

Figure 4: Effective capacitance vs. device volume for h>1.27mm. The influence of the device height on the effective capacitance is illustrated per color. Figure 5: Current vs. volume with illustrated dependency on height.

Figure 5: Current vs. volume with illustrated dependency on height.

Conclusion

A practical solution is presented for the problem, how CDM targets can be translated to current test levels. CDM current test levels are important as they allow using alternative CDM testing methods, such as CCTLP. The first testing proposal is a simple approach, representing the worst case: Increase the CCTLP testing voltage until the peak current value is reached at the product pin given in Figure 5.

To avoid over-testing, these levels can be lowered based on the second proposal if details of the electrical properties on-package and on-chip are known. Ceff values can be predicted by FEM simulation even before devices are available.

The full paper was published in [6].

References

- ANSI/JEDEC/ESDA, “Joint Standard for Electrostatic Discharge Sensitivity Testing – Charged Device Model,” JS-002, 2018

- K. Esmark, R. Gaertner, S. Seidl, F. zur Nieden, H. Wolf and H. Gieser, “Using CC-TLP to get a CDM robustness value,” 2015 37th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Reno, NV, USA, 2015, pp. 1-10.

- B. C. Atwood, Y. Zhou, D. Clarke and T. Weyl, “Effect of large device capacitance on FICDM peak current,” 2007 29th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD),

Anaheim, CA, USA, 2007, pp. 5A.1‑1‑5A.1-10. - N. Jack, B. Carn and J. Morris, “Toward Standardization of Low Impedance Contact CDM,” 2019 41st Annual EOS/ESD Symposium (EOS/ESD), Riverside, CA, USA, 2019, pp. 1-7.

- T. J. Maloney and N. Jack, “CDM Tester Properties as Deduced From Waveforms,” in IEEE Transactions on Device and Materials Reliability, vol. 14, no. 3, pp. 792-800, Sept. 2014, doi: 10.1109/TDMR.2014.2316177

- L. Zeitlhoefler, T. Lutz, F. Zur Nieden, K. Esmark and R. Gaertner, “Voltage to Current Correlation for CDM Testing,” 2023 45th Annual EOS/ESD Symposium (EOS/ESD), Riverside, CA, USA, 2023, pp. 1-11, doi: 10.23919/EOS/ESD58195.2023.10287735